我們想讓你知道:台積電製程領先業界,除了專業分工地位明確,研發團隊全力以赴更是重要原因;未來兩年公司訂單滿載,作者認為是年輕人參與世界級任務的難得機會,不可錯過了。

上週和大家談,台積電是否讓台清交一流人才做二流工作?引發廣大迴響,點閱率破30萬,有網友問我能不能再進一步談談台積電和英特爾、三星的競爭力?為什麼台積電能,英特爾、三星卻不能?讓我們從台積電領先全球的「先進製程」與「先進封裝」二項技術談起,看看台積電領先英特爾、三星的秘密,今天先來談談先進製程。(延伸閱讀:台積電用一流人才做二流工作?專家:多虧這些高手,才能超越英特爾!)

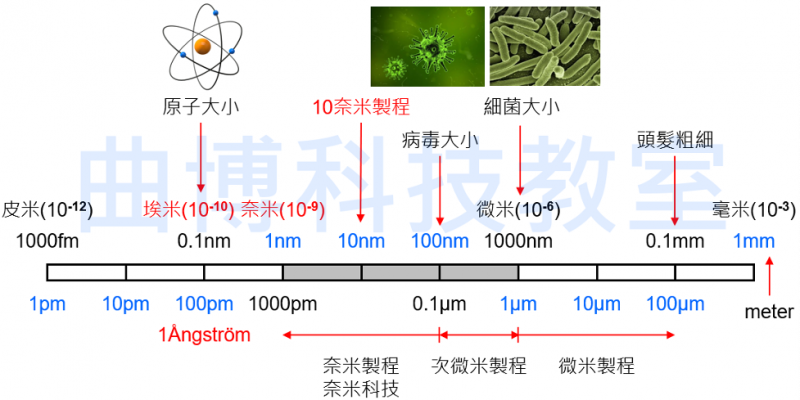

什麼是微米(μm)與奈米(nm)?

我們最常使用的長度單位是「米(m)」,也就是「公尺」,因此:

毫(mini):代表千分之一,「毫米(mm)」代表千分之一米。

微(micro):代表百萬分之一,「微米(μm)」代表百萬分之一米。

奈(nano):代表十億分之一,「奈米(nm)」代表十億分之一米。

因為微小的尺寸看不到,可能大家沒有感覺,我們來舉一些實例,如圖一所示,人類頭髮的粗細大約100微米(μm),細菌的尺寸大約1微米(μm),病毒的尺寸大約100奈米(nm),台積電的製程目前可做到10奈米(nm)以下,大約只有病毒1/10,厲害吧!未來甚至會開發小於1奈米的製程,稱為「次奈米製程」或「埃米製程」,差不多是一顆原子的大小。

什麼是積體電路(IC:Integrated Circuit)?

將電的主動元件(二極體、電晶體)與被動元件(電阻、電容、電感)縮小以後,製作在矽晶圓或砷化鎵晶圓上,稱為「積體電路(IC:Integrated Circuit)」,其中「堆積(Integrated)」與「電路(Circuit)」是指將許多電子元件堆積起來的意思。

將電子產品打開以後可以看到印刷電路板(PCB:Printed Circuit Board)如圖一所示,上面有許多長得很像「蜈蚣」的積體電路(IC),積體電路的尺寸有大有小,我們以處理器為例邊長大約20毫米(mm),上面一小塊正方形稱為「晶片(Chip)」或「晶粒(Die)」,晶片邊長大約10毫米(mm),晶片上面密密麻麻的元件稱為「電晶體(Transistor)」,電晶體邊長大約100奈米(nm),而電晶體上面尺寸最小的結構稱為「閘極長度(Gate length)」大約10奈米(nm),這個就是我們常聽到的台積電「10奈米製程」。(延伸閱讀:台積電小心,最悍對手來了!三星猛砸3.5兆,急起直追搶5奈米訂單)

什麼是場效電晶體(FET:Field Effect Transistor)?

電晶體的種類很多,先從大家耳熟能詳的「MOS」來說明。MOS的全名是「金屬—氧化物—半導體場效電晶體(MOSFET:Metal Oxide Semiconductor Field Effect Transistor)」, 構造如圖二所示,左邊灰色的區域叫做「源極(Source)」,右邊灰色的區域叫做「汲極(Drain)」,中間有塊金屬(紅色)突出來叫做「閘極(Gate)」,閘極下方有一層厚度很薄的氧化物(黄色),因為中間由上而下依序為金屬(Metal)、氧化物(Oxide)、半導體(Semiconductor),因此稱為「MOS」。

MOSFET的工作原理很簡單,電子由左邊的源極流入,經過閘極下方的電子通道,由右邊的汲極流出,中間的閘極則可以決定是否讓電子由下方通過,有點像是水龍頭的開關一樣,因此稱為「閘」;電子是由源極流入,也就是電子的來源,因此稱為「源」;電子是由汲極流出,看看說文解字裡的介紹:汲者,引水于井也,也就是由這裡取出電子,因此稱為「汲」。

當閘極不加電壓,電子無法導通,代表這個元件處於「關(OFF)」的狀態,我們可以想像成這個位元是0,如圖二(a)所示;

當閘極加正電壓,電子可以導通,代表這個元件處於「開(ON)」的狀態,我們可以想像成這個位元是1,如圖二(b)所示。

MOSFET是目前半導體產業最常使用的一種場效電晶體(FET),科學家將它製作在矽晶圓上,是數位訊號的最小單位,我們可以想像一個MOSFET代表一個0或一個1,就是電腦裡的一個「位元(bit)」。電腦是以0與1兩種數位訊號來運算,我們可以想像在矽晶片上有數十億個MOSFET,就代表數十億個0與1,再用金屬導線將這數十億個MOSFET的源極、汲極、閘極連結起來,電子訊號在這數十億個0與1之間流通就可以交互運算,最後得到使用者想要的加、減、乘、除運算結果,這就是電子計算機或電腦的基本工作原理。晶圓廠像台積電、聯電,就是在矽晶圓上製作數十億個MOSFET的工廠。

閘極長度: 半導體製程進步的關鍵

在圖二的MOSFET 中,「閘極長度(Gate length)」大約10奈米,是所有構造中最細小也最難製作的,因此我們常常以閘極長度來代表半導體製程的進步程度,這就是所謂的「製程節點(Node)」。閘極長度會隨製程技術的進步而變小,從早期的0.18、0.13微米,進步到90、65、45、22、14奈米,到目前最新的製程10、7、5奈米,甚至未來的3奈米。當閘極長度愈小,則整個MOSFET就愈小,而同樣含有數十億個MOSFET的晶片就愈小,封裝以後的積體電路(IC)就愈小,最後做出來的手機就愈小囉!

鰭式場效電晶體(FinFET):將半導體製程帶入新境界

MOSFET的結構發明以來到現在已使用超過四十年,當閘極長度縮小到20奈米以下的時候遇到了許多問題,其中最麻煩的就是當閘極長度愈小,源極和汲極的距離就愈近,閘極下方的氧化物也愈薄,電子有可能偷偷溜過去產生「漏電(Leakage)」;另外一個更麻煩的問題,原本電子是否能由源極流到汲極是由閘極電壓來控制的,但是閘極長度愈小,則閘極與通道之間的接觸面積愈小,如圖三(a)綠色箭頭所示,也就是閘極對通道的影響力愈小,要如何才能保持閘極對通道的影響力(接觸面積)呢?

因此美國加州大學伯克萊分校胡正明、Tsu-Jae King-Liu、Jeffrey Bokor等三位教授發明了「鰭式場效電晶體(FinFET:Fin Field Effect Transistor)」,把原本2D構造的MOSFET改為3D的FinFET,如圖三(b)綠色箭頭所示,因為構造很像魚鰭 ,因此稱為「鰭式(Fin)」。

由圖中可以看出原本的源極和汲極拉高變成立體板狀結構,讓源極和汲極之間的通道變成板狀,則閘極與通道之間的接觸面積變大了,這樣一來即使閘極長度縮小到20奈米以下,仍然保留很大的接觸面積,可以控制電子是否能由源極流到汲極,因此可以更妥善的控制電流,同時降低漏電和動態功率耗損,所謂動態功率耗損就是這個FinFET由狀態0變1或由1變0時所消耗的電能,降低漏電和動態功率耗損就是可以更省電的意思囉!

胡正明教授曾任台積電技術執行長,現在大家知道台積電為什麼在FinFET製程會領先英特爾和三星了吧!但是要記得,把FinFET的技術帶進台積電是一回事,要把良率做高是另外一回事,台積電領先英特爾和三星最明顯的還是良率,這個和晶圓材料的品質、特用化學品的純度、製程參數的控制等息息相關,是整個團隊共同努力的成果。(延伸閱讀:晶片龍頭只有英特爾?AMD和英偉達藉收購案發起挑戰)

這裡要特別注意,一般我們說的65、45奈米在MOSFET上是指「閘極長度」,但是到了14、10、7、5奈米在FinFET上指的其實是概念上的「平均長度」,只能當做是商品名稱,而不是真的閘極長度,這主要是因為FinFET電晶體的結構比較複雜,因此各家廠商都定義了各自不同的「平均長度」計算方式,所以當我們聽到英特爾、台積電、三星的「10奈米」製程,許多人都把它們當成同一個東西拿來比較,其實這樣比較是不正確的。

環繞閘極場效電晶體(GAAFET):未來先進製程的發展方向

大家猜猜,當閘極長度縮小到3奈米以下的時候,還有什麼辦法可以增加閘極與通道之間的接觸面積?就是閘極把電子通道完全包圍起來,如圖三(c)所示,稱為「環繞閘極場效電晶體(GAAFET:Gate All Around Field Effect Transistor)」。GAA的原理其實很簡單,就是增加閘極與電子通道的接觸面積,可以增加閘極控制效果,這麼簡單的道理,當然不會只有三星的人想到,事實上台積電、英特爾早就在發展各自的GAA,只是結構稍有不同而已。

實際上GAA遇到許多製程方面的困難,目前大家都遇到良率的問題無法量產,而且「水平式」的GAA和FinFET性能其實差異不大,必須製作「垂直式」的GAA效果才明顯,而垂直式製程極為困難,三星展出的GAA其實只是水平式的而己,還有報導說什麼三星想用GAA在3奈米彎道超車台積電,只能說不是媒體的想像力太豐富,就是三星的行銷比較厲害!台積電已經決定3奈米先用FinFET,是比較穩妥的做法。(延伸閱讀:就是他!年領2700萬美元卻耽誤Intel 7奈米製程,資深女將接手力拚AMD)

英特爾、台積電、三星製程大PK

要增加閘極與通道接觸面積也可以使用「多鰭式場效電晶體(Multi FinFET)」的結構,如圖四(b)所示,這個結構其實已經用很久了!理論上當製程節點愈小,則FinFET就愈小,而同樣含有十億個FinFET的晶片就愈小,事實上並非如此。

如表一所示,同樣是10奈米製程,由於鰭片間距、閘極間距、最小金屬間距不同,造成英特爾製作的電晶體尺寸比台積電與三星還要小,例如:圖四(c)的鰭片間距是34奈米(nm),因此電晶體密度是英特爾:台積電:三星大約100:60:52。意思是:英特爾的10奈米製程,實際上的電晶體尺寸和台積電或三星的7奈米差不多,這就是為什麼英特爾常說大家使用製程節點來比較三家廠商的技術對他們來說不公平。

台積電、三星、英特爾先進製程進度如表二所示,2020年台積電量產5奈米製程,三星雖然也號稱量產5奈米,實際上只是7奈米的改良版,而且高通驍龍888使用三星5奈米製程發生過熱問題,耗電量甚至超過台積電的7奈米製程,雖然ARM Cortex-X核心比較耗電,但是三星的製程顯然與台積電相比仍然有不小的差距,手機產品對功耗要求嚴格,因此手機晶片客戶將會大量轉單台積電,造成台積電未來兩年訂單大爆滿,今年增加擴廠對人才需求很大,我鼓勵年輕朋友不要害怕吃苦,應該勇敢接受挑戰,利用這個機會參與這場全球半導體先進製程大戰。(延伸閱讀:急!連台積電都喊缺工 昔日熱門資訊工程科系11年來竟銳減5萬學生)

雖然英特爾(Intel)的7奈米製程,相當於台積電的5奈米製程,原本計畫2021年量產只落後台積電5奈米製程一年,但是2021年新任執行長上台後已經宣布延後到2023年量產,一下子落後台積電三年,而10奈米產能不足造成缺貨,桌上型電腦市場被超微(AMD)領先,筆記型電腦市場也岌岌可危。目前對英特爾最有利的方式是「立刻」將中低階產品外包給台積電,以相同的製程打敗超微奪回市場,同時替自己爭取兩年時間協調晶圓廠與設計部門把先進製程的問題解決。(延伸閱讀:電機系出路廣,資工系價值高,差異到底在那裡?)

為什麼要強調「立刻」,因為就算英特爾要外包,台積電目前也沒有產能,而且積體電路設計圖與晶圓代工製程相關,英特爾將產品外包給台積電必須修改設計圖,至少也需要大約一年的時間,因此就算現在立刻決定最快也要到2022年才能量產,每拖一天對英特爾都是損失,新任執行長是工程背景,對於協調晶圓廠與設計部門把先進製程的問題解決應能勝任,只是需要時間,這時候以商業考量外包台積電是最好的選擇。

作者為台大電機博士,知識力專家社群創辦人。

責任編輯/周岐原

◎加入《下班經濟學》粉絲團,給你更多財經資訊

◎訂閱《下班經濟學》YouTube頻道,精彩節目不錯過